I ricercatori del MIT hanno sviluppato un nuovo tipo di transistor tridimensionale utilizzando materiali semiconduttori ultrasottili, in grado di superare i limiti fondamentali dei tradizionali transistor in silicio. Il dispositivo promette prestazioni paragonabili ai transistor in silicio più avanzati, ma operando a voltaggi molto inferiori e con maggiore efficienza energetica.

Questa innovazione potrebbe avere un impatto sull'industria elettronica, consentendo di realizzare chip più potenti ed efficienti per computer, smartphone e altri dispositivi. Il superamento della cosiddetta "tirannia di Boltzmann", che limita l'efficienza dei transistor in silicio, apre nuove possibilità per l'evoluzione delle tecnologie computazionali, soprattutto in vista della crescente domanda di calcolo legata all'intelligenza artificiale.

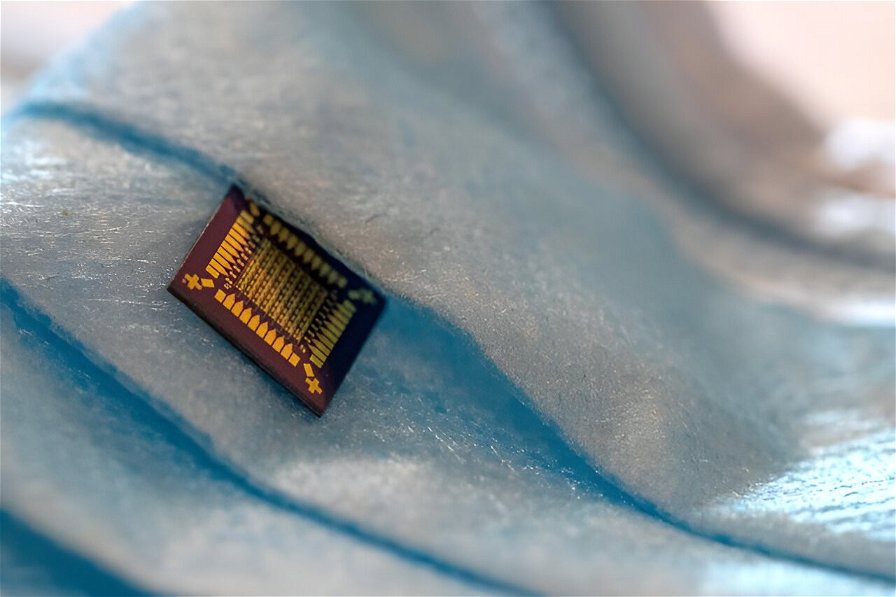

I nuovi transistor sfruttano le proprietà quantistiche dei materiali per ottenere contemporaneamente basso voltaggio operativo e alte prestazioni in un'area di pochi nanometri quadrati. La loro struttura tridimensionale con nanofili verticali ultrasottili permetterebbe di impacchettare un numero molto maggiore di transistor su un singolo chip.

"Con questa tecnologia si potrebbero ottenere tutte le funzionalità attuali del silicio, ma con un'efficienza energetica molto superiore", spiega Yanjie Shao, ricercatore post-dottorato del MIT e autore principale dello studio pubblicato su Nature Electronics.

I ricercatori hanno utilizzato una combinazione di materiali semiconduttori come l'antimoniuro di gallio e l'arseniuro di indio, progettando i dispositivi per sfruttare il fenomeno quantistico dell'effetto tunnel. Ciò consente agli elettroni di attraversare la barriera energetica anziché scavalcarla, permettendo una commutazione più rapida ed efficiente del transistor.

La realizzazione di questi minuscoli dispositivi ha richiesto tecniche di fabbricazione estremamente precise. Utilizzando le strutture all'avanguardia del MIT.nano, i ricercatori sono riusciti a controllare con precisione la geometria 3D dei transistor, creando nanostrutture verticali con un diametro di soli 6 nanometri.

Questa ingegnerizzazione così accurata ha permesso di ottenere simultaneamente una ripida pendenza di commutazione e un'elevata corrente, sfruttando il fenomeno del confinamento quantistico. "Abbiamo molta flessibilità nel progettare queste eterostrutture di materiali in modo da ottenere una barriera tunnel estremamente sottile, che ci consente di raggiungere correnti molto elevate", afferma Shao.

I test sui dispositivi hanno mostrato una pendenza di commutazione inferiore al limite fondamentale raggiungibile con i transistor in silicio convenzionali, con prestazioni circa 20 volte superiori rispetto a transistor tunnel simili.

Il team sta ora lavorando per migliorare i metodi di fabbricazione e ottenere transistor più uniformi su un intero chip. Data l'estrema miniaturizzazione, anche variazioni di 1 nanometro possono influenzare significativamente il comportamento degli elettroni.

I ricercatori stanno inoltre esplorando strutture verticali a forma di pinna, oltre ai nanofili verticali, che potrebbero potenzialmente migliorare l'uniformità dei dispositivi su un chip.

Secondo Aryan Afzalian, ricercatore presso l'organizzazione di ricerca nanoelettronica imec non coinvolto nello studio, "questo lavoro va decisamente nella giusta direzione, migliorando significativamente le prestazioni dei transistor a effetto tunnel. Dimostra una pendenza ripida insieme a una corrente di pilotaggio da record, evidenziando l'importanza di dimensioni ridotte, confinamento estremo e materiali e interfacce a bassa difettosità."

Sebbene ci siano ancora molte criticità da superare prima di una possibile commercializzazione, questa ricerca rappresenta sicuramente un importante passo avanti concettuale verso transistor più efficienti ed avanzati.