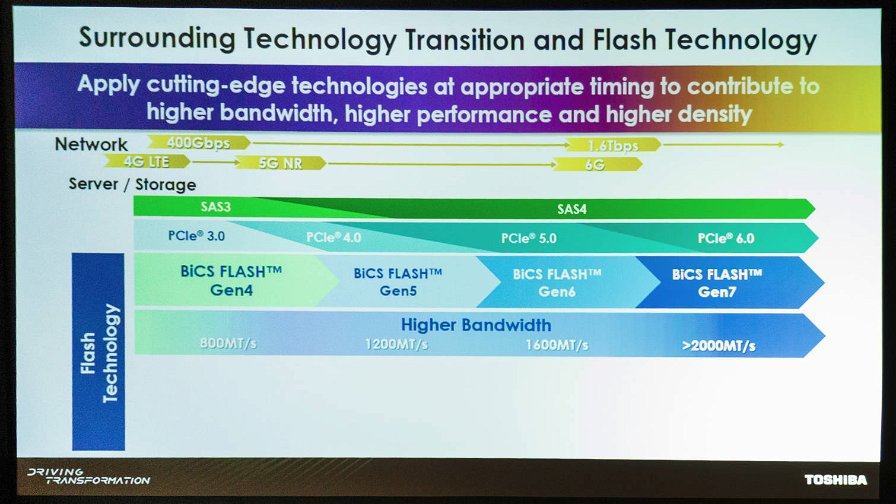

Nel corso del Flash Memory Summit la giapponese Toshiba ha illustrato i suoi piani per il futuro per quanto riguarda le memorie a stato solido del futuro. Dopo aver messo a punto la quarta generazione della memoria 3D NAND, nota come BICS 4, l’azienda ha iniziato a pensare alle successive versioni, fino alla settima generazione.

Ogni generazione coinciderà con nuove generazioni dello standard PCI Express, e ciò inizierà con le BiCS 5 che arriveranno sul mercato presto allineandosi con il PCIe 4.0, anche se Toshiba non ha indicato una timeline specifica.

Le BiCS 5 avranno un bandwidth più elevato pari a 1200 MT/s, mentre le BiCS 6 raggiungeranno 1600 MT/s e le BiCS 7 si spingeranno fino a 2000 MT/s.

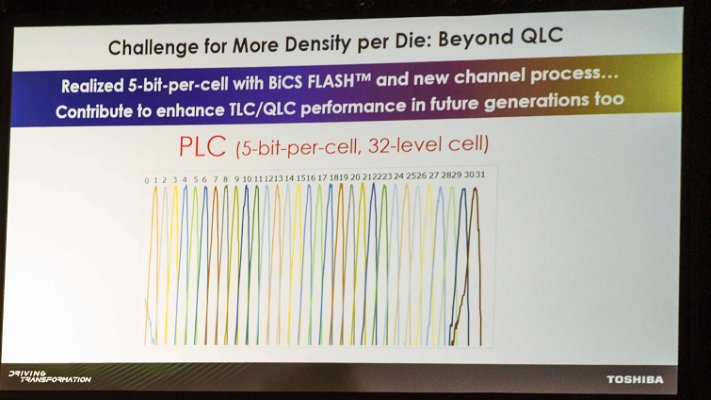

Toshiba ha inoltre iniziato a fare ricerca sulla NAND flash Penta-level Cell (PLC), ossia capace di archiviazione fino a 5 bit d’informazione per cella. L’azienda attualmente ha iniziato a lavorare sulla NAND a 5 bit modificando l’attuale QLC (4 bit per cella).

Un bit in più per cella assicura maggiore densità, ma per farlo la cella deve essere in grado di archiviare 32 distinti livelli di tensione e i controller degli SSD devono essere ottimizzati per leggerli in modo accurato.

Altri elementi di cui tenere conto sono le prestazioni e la resistenza alla scritture: l’attuale memoria QLC è più lenta e meno resistente degli altri tipi di memorie. La PLC avrà resistenza e prestazioni persino inferiori.

Nuove funzionalità del protocollo NVMe come Zoned Namespaces (ZNS) dovrebbero aiutare a mitigare alcuni problemi. ZNF di per sé riduce la write amplification, riducendo la necessità dell’over-provisioning e l’uso della DRAM interna al controller, migliorando throughput e latenza.

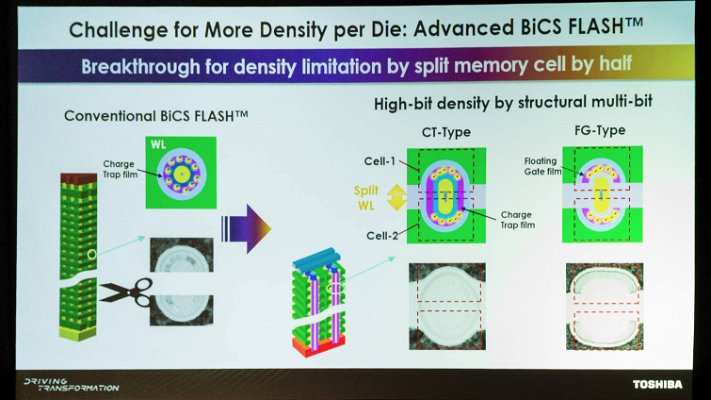

Toshiba ha inoltre sviluppato un nuovo processo che aumentare la densità dei die nella prossima generazione di BICS flash. Essenzialmente suddividerà la cella di memoria a metà per scalare verso l'alto, mantenendo i tradizionali processi produttivi. L’azienda non è comunque sicura al momento che questo approccio sia la strada giusta da seguire in questo momento.

Per quanto concerne la XL-Flash, memoria annunciata lo scorso anno che rappresenta la risposta alla Z-NAND di Samsung e a Intel Optane (3D XPoint), Toshiba ha messo a punto un die da 128 gigabit disponibile in package con 2, 4 e 8 die, con un’architettura a 16 piani per un maggiore parallelismo. Secondo l’azienda la latenza in lettura della XL-Flash è inferiore a 5 microsecondi, ovvero è circa 10 volte più veloce rispetto alla TLC.

XL-Flash è sostanzialmente una forma di NAND SLC che è stata ottimizzata per tempi di risposta migliori. Toshiba la userà negli SSD, ma prevede anche un’applicazione come NVDIMM. I primi sample sono stati realizzati, e le consegne inizieranno a settembre, mentre la produzione di massa è prevista nel 2020.