Le future architetture Intel Meteor Lake, Arrow Lake e Lunar Lake introdurranno diverse novità, a cominciare dal modo in cui verranno costruite. Oltre all'utilizzo di un design MCM (Multi Chip Module), le nuove CPU faranno per la prima volta uso della tecnologia di packaging 3D Foveros, introdotta nel 2019 su alcune FPGA e GPU destinate agli ambiti HPC. L'azienda ha svelato alcuni dettagli su come intende usarla nei prossimi processori in un'anteprima dell'evento "Hot Chips 34", una conferenza dove le figure di spicco del settore dei semiconduttori condividono i più recenti sviluppi tecnologici.

Stando alle precedenti informazioni, tre delle quattro tile che includeranno la connettività, il SoC e la GPU dei processori Meteor Lake verranno prodotte da TSMC, mentre quella restante che riguarda la CPU, come condiviso da fonti interne al settore, utilizzerà il nodo proprietario Intel 4. Nonostante la casa non abbia mai svelato ufficialmente il processo produttivo utilizzato dal partner taiwanese, recenti indiscrezioni parlavano di possibili ritardi causati dal passaggio al nodo 5nm, voci in seguito smentite dall'azienda stessa, la quale ha precisato che questo non è mai cambiato e che l'architettura è sulla buona strada per rispettare il lancio previsto nel 2023. Secondo informazioni in merito, le tile SOC e I/O dovrebbero nello specifico utilizzare il nodo N6, mentre la tGPU (ossia la tile grafica) sarà fabbricata con il nodo N5.

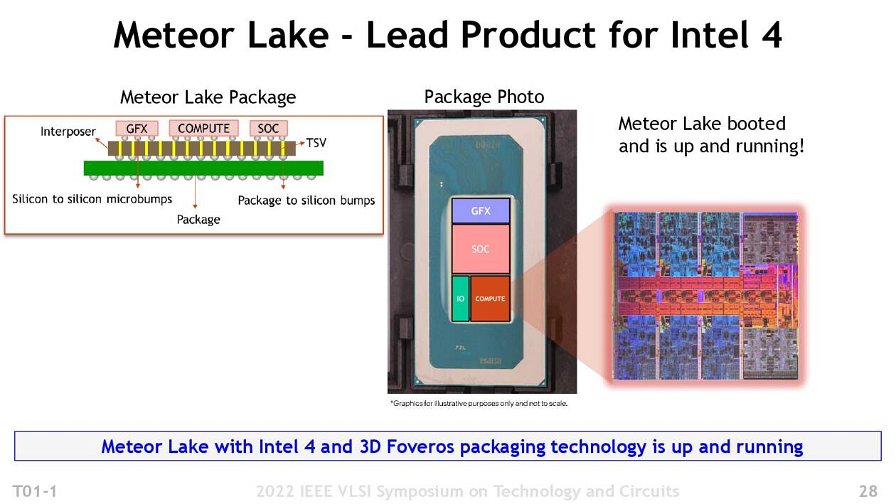

Come è possibile vedere nella diapositiva condivisa da Intel, che raffigura un die Meteor Lake destinato ai portatili e dotato di una configurazione di core 6P+2E, la tecnologia 3D Foveros consentirà all'azienda di impilare verticalmente i componenti del die, che verranno posizionati sopra un interposer che fornirà l'interconnessione unificata tra i chiplet. Gli interconnettori sferici che vedete tra gli elementi sono chiamati "microbumps", che metteranno in comunicazione i diversi elementi e avranno una dimensione nell'ordine dei 36 micron. L'interposer sarà realizzato da Intel tramite il suo processo 22FFL, un nodo a basso costo ottimizzato per i circuiti a bassa potenza.

La tecnologia 3D Foveros è stata impiegata per la prima volta dall'azienda nelle FPGA Agilex, oltre che le GPU Ponte Vecchio e Rialto Bridge. L'iterazione più recente, che verrà introdotta da Meteor Lake in poi, differisce per l'utilizzo di microbumps più piccoli rispetto quelli da 55 micron dei precedenti prodotti. La tabella di marcia prevede il raggiungimento dei 18 micron nelle prossime architetture, servendosi in futuro di interconnessioni HBI (Hybrid Bonding Interconnection) per arrivare a 1 micron.

La tecnologia è stata progettata da Intel per essere la più economica possibile, ciò consentirà di abbattere ulteriormente i costi di progettazione e produzione, sposandosi alla perfezione con il design multi chiplet. A partire da Arrow Lake inoltre, le CPU utilizzeranno l'interconnessione standardizzata UCIe così da essere ancora più semplici da realizzare.