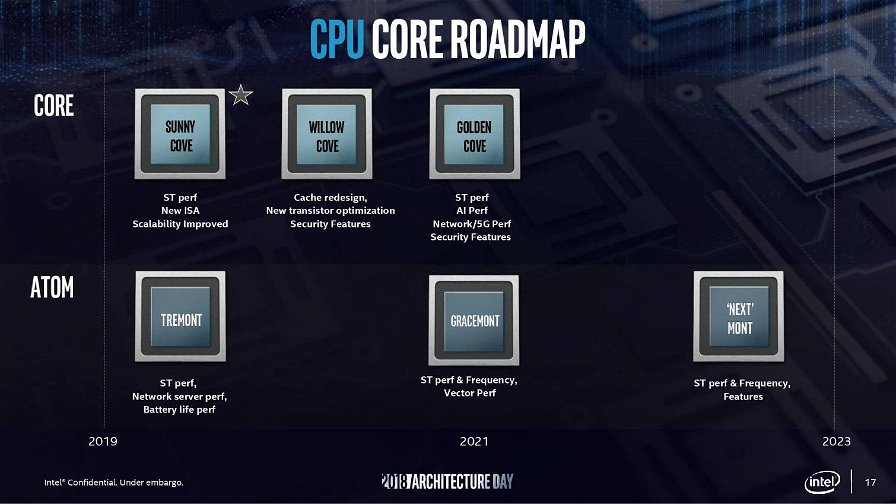

Snow Ridge, il prossimo SoC 5G di Intel per le base station, prodotto a 10 nanometri, sarà basato su architettura x86 Tremont (Atom) e userà l'architettura di interconnessione mesh al posto del più tradizionale ring bus.

Questi dettagli sono emersi grazie a un recente tweet dell'ingegnere di Intel Mark Ermolov, in cui è stato pubblicato un manuale contenente un diagramma del SoC Snow Ridge e altri particolari.

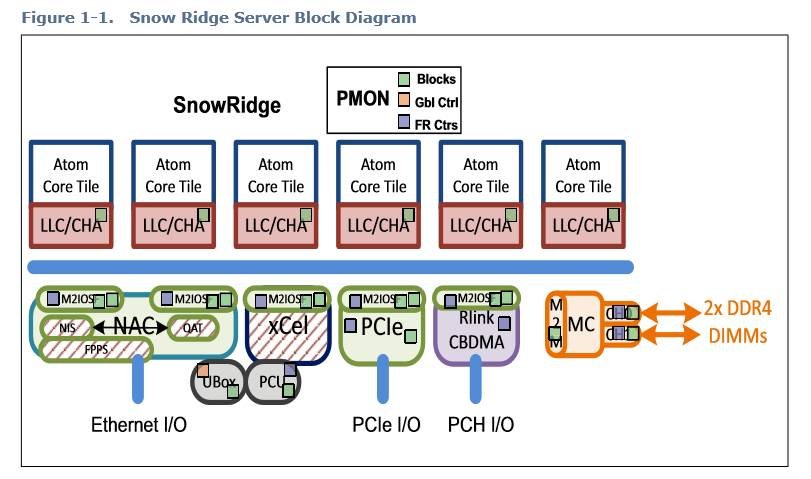

Il diagramma mostra 6 tile Atom, ciascuno con la propria last level cache (LLC). Poiché si tratta di un SoC a 10 nanometri, probabilmente il chip è basato sulla nuova architettura Atom "Tremont", che ritroviamo anche in chip come Lakefield. In termini di connettività c'è la Ethernet, supporto per la memoria DDR4 dual-channel grazie a un controller integrato con supporto ECC e il PCI Express 3.0.

La scelta di usare l'architettura di connettività mesh, introdotta nel 2016 con le soluzioni Xeon Phi (Knights Landing) e con Skylake-SP nel 2017 sul fronte Xeon, è probabilmente da ricollegarsi alla presenza di un alto numero di core.

Il diagramma mostra tuttavia solo sei tile. Nei prodotti Xeon Phi una singola tile contava due core Atom e se ciò si confermasse vero anche per Snow Ridge, allora il numero dei core salirebbe a 12. È tuttavia possibile che con l'architettura Tremont Intel abbia esteso il numero dei core a 4, o forse il diagramma non rappresenta il massimo numero di tile.

Una nota sotto al diagramma riporta infatti: "questo diagramma rappresenta una possibile configurazione. Il numero di core e slice LLC supportati varia in base alla singola unità. Non tutte le funzionalità sono supportate dai singoli chip".

Per saperne di più non dovremo far altro che attendere: a differenza di quanto dichiarato inizialmente da Intel, la data di lancio di Snow Ridge è slittata dalla seconda metà 2019 al primo trimestre 2020.