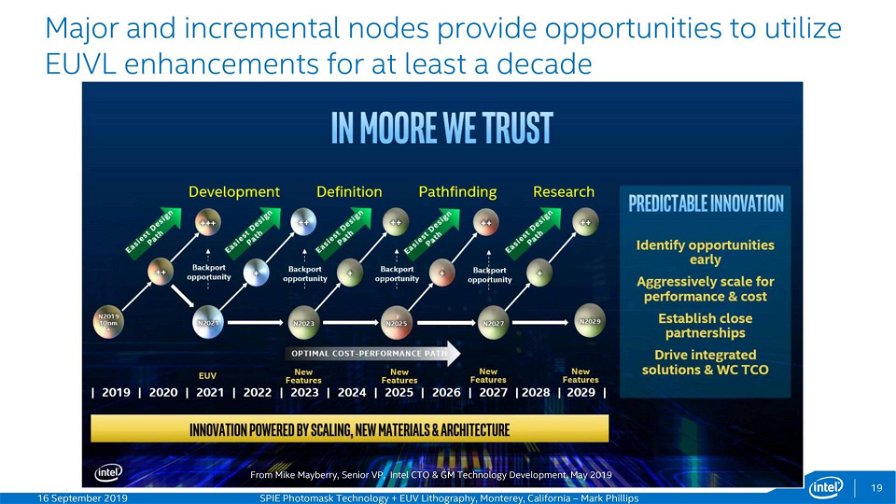

Con quale processo produttivo saranno realizzate le CPU di Intel nel 2029? 1,4 nanometri, secondo una slide mostrata da ASML, produttore olandese di macchinari litografici, nel corso della conferenza IEEE International Electron Devices Meeting (IEDM).

ASML ha presentato per l’occasione una versione alterata di una slide ufficiale di Intel, andando a sostituire le date indicate dall’azienda nella parte inferiore con i processi produttivi specifici. Per questo motivo vedete entrambe le slide nell’articolo.

Stando a quanto riportato da alcuni media statunitensi (es. Anandtech), quanto indicato nella slide modificata rimane rilevante e quindi rappresentativo delle intenzioni future della casa di Santa Clara. Come si può vedere, e come già indicato da Intel in passato, l’obiettivo è avanzare di processo produttivo ogni 2 anni, partendo dai 10 nanometri che effettivamente l’azienda ha adottato quest’anno con le CPU mobile Ice Lake.

D’altronde la slide dice chiaramente “In Moore we trust”, ossia Intel vuole continuare a rispettare la cosiddetta legge di Moore (“Il numero di transistor raddoppia ogni 18/24 mesi”, con varie altre declinazioni e/o storture).

Nel 2021 ecco il salto ai 7 nanometri (con l’introduzione della litografia EUV - ultravioletto estremo), per poi passare ai 5 nanometri nel 2023, ai 3 nanometri nel 2025, i 2 nanometri nel 2027 e gli 1,4 nanometri nel 2029. Quest’ultimo è equivalente a una dimensione di 12 atomi.

Come fa notare Anandtech, per quanto si parli di una miniaturizzazione estrema, l’industria sta discutendo da diverso tempo di dimensioni persino inferiori, ad esempio allo IEDM si è toccato il tema degli 0,3 nanometri con materiali 2D autoassemblanti, e ovviamente sono tanti gli ostacoli sul percorso di Intel e i suoi partner.

Per affrontare le richieste di mercato e crearsi un’utile scialuppa di salvataggio in caso di eventuali problemi nell’avanzamento di processo produttivo – pensate a quanto sta avvenendo con i 14 nanometri – Intel creerà due versioni migliorate di ogni processo.

Con l’eccezione dei 10 nanometri, che sono già indicati come 10+ e a cui seguiranno le versioni 10++ (2020) e 10+++ (2021), vedremo un processo di base, seguito da una versione migliorata l’anno successivo (+) e una ulteriormente affinata dopo due anni (++). Nella slide compare una dicitura piuttosto interessante, “backporting opportunity”, che è necessario spiegare.

Non si tratta di qualcosa di inedito, infatti vuol dire semplicemente che se un chip viene pensato per un dato processo produttivo (ad esempio i 5 nanometri) ma si incontrano problemi, è possibile realizzarlo con la versione “++” del processo precedente (nell’esempio fatto, i 7 nanometri “++”).

Intel ha dichiarato già da diverso tempo che l’obiettivo è quello di tagliare il cordone ombelicale che sinora ha legato in modo indissolubile i vari progetti a specifici processi produttivi. Riuscirà Intel a mantenere la cadenza e i suoi obiettivi? Solo il tempo ce lo dirà, ma è utile ricordare che non c’è un unico team che sviluppa tutti i processi, quindi pensate a diversi gruppi di persone che lavorano in parallelo per fissare le caratteristiche e tutto ciò che serve per produrre con un determinato processo.

La slide indica che Intel in questo momento sta mettendo a punto le ottimizzazioni del processo 10+++ e lavorando sui 7 nanometri e le sue declinazioni. Un’altra informazione che emerge è che i 7 nanometri sono basati sui 10++, mentre i 5 nanometri evolveranno partendo dai 7 nanometri e così via, anche se è plausibile che alcune delle ottimizzazioni dei processi "+" e "++" finiranno anche nei processi produttivi principali.

Per quanto riguarda i processi a partire dal 2023, Intel è attualmente in modalità “path finding”, ossia sta cercando un percorso, ovvero provando a capire concretamente cosa le serve per arrivare a quel tipo di miniaturizzazione. Oltre si parla di “research”, ricerca, con l’azienda che studia nuovi materiali, design di transistor (gate-all-around, nano-sheet, nano-wire, ecc.) e qualsiasi cosa potrebbe essere applicata a quei processi.