Nel corso dell'evento Next Horizon a cui siamo presenti in quel di San Francisco, AMD ha annunciato la seconda generazione dei processori EPYC, prodotta con il processo produttivo a 7 nanometri di TSMC e migliorata dall'architettura Zen 2. Partiamo proprio dall'architettura Zen 2, attualmente in fase di sampling, che vede proprio nel processo produttivo una parte fondamentale delle proprie qualità.

I 7 nanometri permettono di raddoppiare la densità, di migliorare i consumi di 0,5 volte (a parità di prestazioni) e di migliorare le prestazioni di oltre 1,25 volte (a parità di consumi). Per quanto riguarda le prestazioni, AMD parla di un throughput fino a 2 volte maggiore, ottenuto grazie a una execution pipeline migliorata, un raddoppio delle prestazioni in virgola mobile e un front-end rinnovato, con un branch predictor e una cache istruzioni riprogettati.

Si parla anche di un'ampiezza delle unità floating point raddoppiata a 256 bit. Stesso discorso per il bandwidth load/store. AMD ha inoltre aumentato il bandwidth dispatch / retire e mantenuto un throughput elevato in tutte le modalità. Sul fronte della sicurezza, la casa di Sunnyvale assicura di aver mitigato in hardware la vulnerabilità Spectre e ulteriormente rafforzato le difese software contro gli altri attacchi alle CPU.

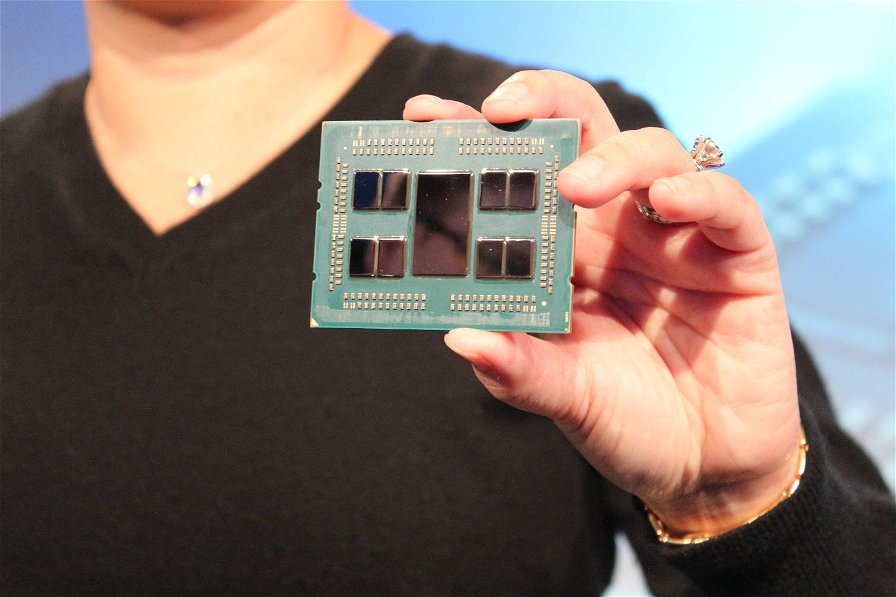

Tutto questo rappresenta la base dei processori EPYC di seconda generazione, sul mercato nel 2019. Laddove la prima generazione a 14 nanometri - nome in codice Naples - conta su un massimo di 32 core e 64 thread ottenuti grazie all'unione di quattro die Zeppelin dotati di otto core ciascuno (due CCX), la seconda generazione "Rome" adotta un progetto differente.

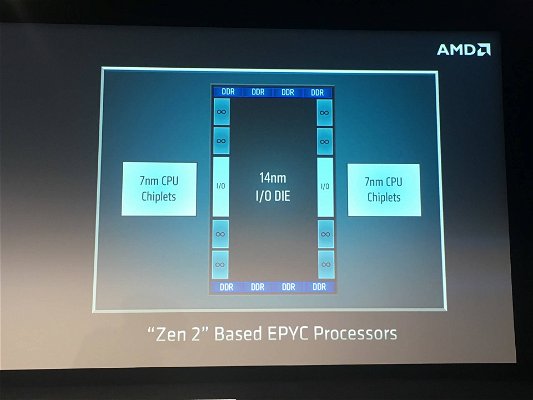

Ci troviamo nuovamente davanti a un approccio MCM (multi-chip module), in cui l'interconnessione ad altissima velocità Infinity Fabric continua a farla da padrona, ma le differenze sono molteplici, anche se le CPU continuano a essere compatibili con il socket SP3, quindi basterà aggiornare il firmware per installare i nuovi EPYC sulle motherboard esistenti (con delle rinunce, chiaramente). AMD ha promesso anche che le piattaforme attuali saranno compatibili con la terza generazione Milan.

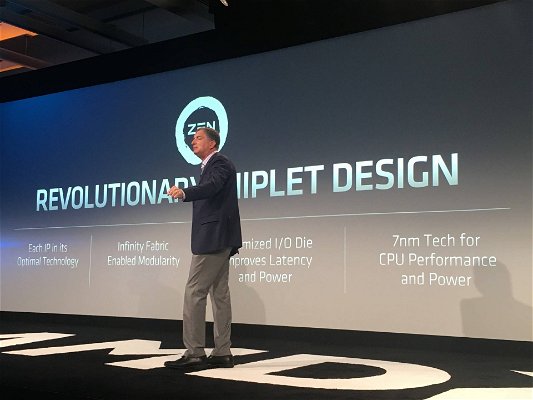

Questa volta abbiamo al centro di tutto un die di input / output prodotto a 14 nanometri (I/O die) circondato da otto "chiplet" realizzati a 7 nanometri, dotati di 8 core ciascuno. Insomma, come potete vedere anche dall'immagine, ci sono 9 chip in totale.

Dei chiplet vi avevamo già parlato in passato e si tratta essenzialmente delle unità in cui trovano posto i core. L'I/O die invece si occupa di tutta la parte di connettività e di scambio dati tra i chiplet e il resto del sistema, migliorando latenza e al tempo stesso anche i consumi. I/O die e core comunicano tra loro tramite Infinity Fabric.

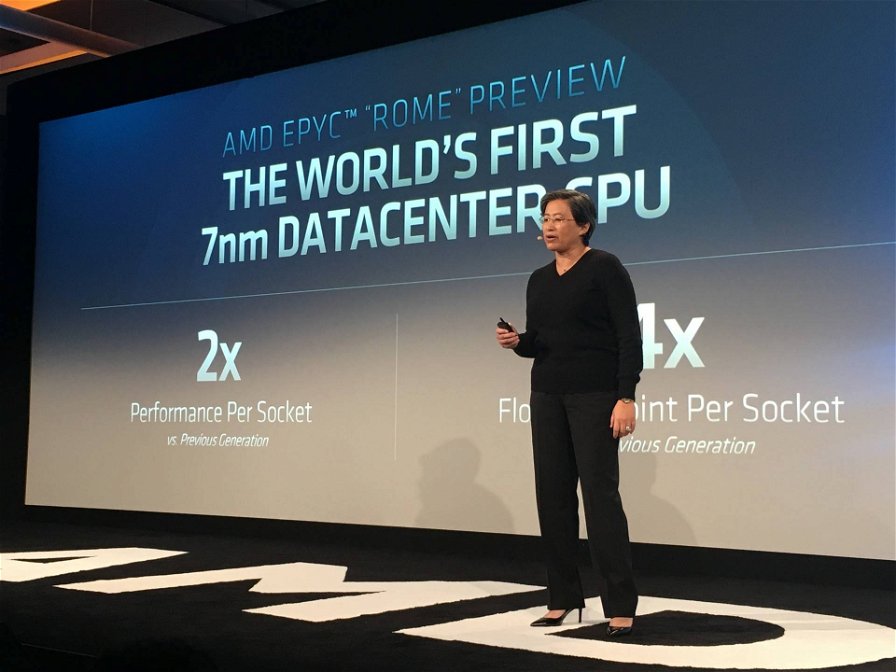

Calcolatrice alla mano un EPYC di seconda generazione "top di gamma" offre 64 core x86 (con SMT per un totale di 128 thread) capaci di garantire prestazioni per socket 2 volte maggiori rispetto alla prima generazione di EPYC. Si parla anche di prestazioni per socket quattro volte maggiori nei calcoli in virgola mobile sempre rispetto ai primi EPYC. Il tutto grazie anche a prestazioni IPC superiori (non quantificate al momento) e un raddoppio del bandwidth per canale. La CPU è dotata di 128 linee PCI Express 4.0 e può supportare fino a 4 TB di RAM in server single socket tramite otto canali di memoria DDR4.

Interessante la dimostrazione live fatta da AMD, dove una piattaforma EPYC single-socket ha battuto una Intel Xeon Scalable 8180M dual-socket nel benchmark industriale C-Ray: la piattaforma Rome ha completato il carico in 28,1 secondi, mentre i due 8180M ci hanno messo 30,2 secondi. AMD ha dichiarato che la piattaforma Rome è stata raffreddata ad aria, non overcloccata e soprattutto lavorava a frequenze non finali.

Da segnalare inoltre che l'annuncio dei nuovi EPYC è stato accompagnato da una nuova partnership siglata da AMD con Amazon AWS, che adotterà le CPU server dell'azienda per i propri servizi di cloud computing EC2 tramite le istanze R5a, M5a e T3a.

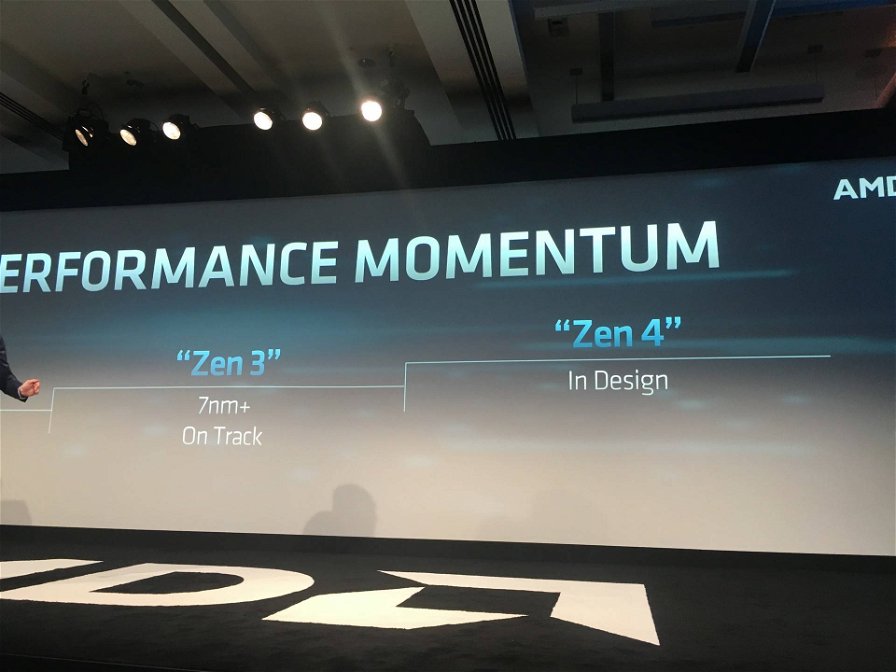

Zen 4 è già in sviluppo

In passato AMD aveva dichiarato di essere già al lavoro sull'architettura Zen 5, quindi non sorprende che durante l'evento Next Horizon l'azienda abbia confermato la roadmap già nota, sottolineando che l'architettura Zen 4 in è in fase di progettazione. Questa architettura sarà preceduta nel 2020 da Zen 3, modellata sul processo produttivo a 7 nanometri plus (7nm+) e da cui prenderà forma la terza generazione EPYC "Milan", che secondo il CEO di AMD Lisa Su è in "profondo sviluppo".

[tomsgallery id=515769]