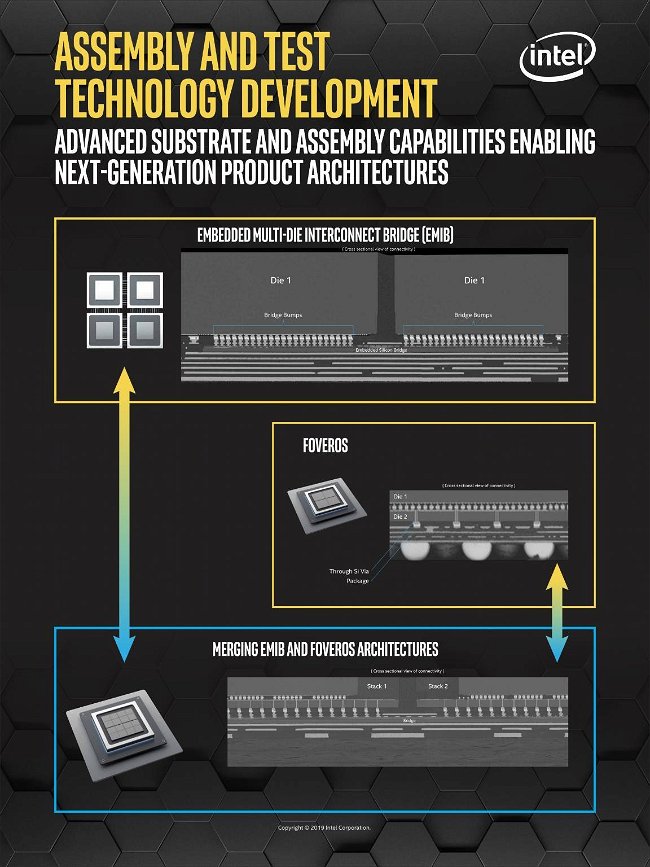

Nel corso del SEMICON West di San Francisco, gli ingegneri di Intel hanno rilasciato alcuni aggiornamenti importanti sulle tecnologie di packaging e sui nuovi blocchi base che andranno a costituire le fondamenta dei suoi futuri microprocessori. EMIB, Foveros e la nuova tecnologia Omni-Directional Interconnect (ODI) gli argomenti al centro del dibattito, ma non solo.

Anche se spesso si parla di processi produttivi - a ragione - anche le tecnologie di packaging del chip giocheranno un ruolo sempre più importante in futuro. Trattandosi dell’interfaccia fisica tra il processore e la motherboard, il package è la zona in cui giungono i segnali elettrici del chip e l’alimentazione, ed è quindi cruciale in un mondo in cui chip diventano sempre più complessi e potenti.

“È più che il passaggio finale del processo di produzione, il packaging è diventato il catalizzatore per l’innovazione di un prodotto. Le tecniche di packaging avanzate permettono l’integrazione di diversi engine di calcolo su più processi produttivi con parametri prestazionali simili a un singolo die, ma con lo scopo della piattaforma che supera di gran lunga i limiti di dimensione di un’integrazione a singolo die”.

“Queste tecnologie miglioreranno le prestazioni a livello di prodotto, i consumi e l’area richiesta favorendo un completo ripensamento dell’architettura di sistema”, ha sottolineato Intel.

La prima novità prende il nome di Co-EMIB. Le tecnologie EMIB e Foveros si affidano a interconnessioni ad alta densità per permettere un bandwidth elevato a basso consumo, garantendo una densità di I/O simile o migliore rispetto ad altri approcci simili. Co-EMIB consente di avere persino maggiori prestazioni di calcolo e capacità.

https://www.youtube.com/watch?v=NZ8t2zdTo2cCo-EMIB permette l’interconnessione di due o più elementi Foveros garantendo essenzialmente le prestazioni di un singolo chip. I progettisti possono inoltre collegare blocchi analogici, di memoria e altri componenti con un bandwidth molto elevato e un consumo molto basso.

ODI, Omni-Directional Interconnect, nasce per fornire ancora più flessibilità nella comunicazione tra i chiplet in un package. Il chip superiore può comunicare orizzontalmente con altri chiplet, in modo simile a EMIB. Può inoltre comunicare tramite TSVs (through-silicon vias) in verticale nel die base sottostante, in modo simile a Foveros. ODI si affida a grandi collegamenti verticali per consentire il passaggio di energia verso il die superiore direttamente dal substrato del package.

ODI offre minore resistenza, garantendo quindi bassa latenza, un bandwidth più alto e un’erogazione di energia maggiore lungo lo stacking di chip. Allo stesso tempo questo approccio riduce il numero di TSV richiesto alla base del die, liberando più area per transistor attivi e ottimizzando la dimensione del die.

https://www.youtube.com/watch?v=JZt4rqzGuHsMDIO è invece una nuova interfaccia “die to die”, nata come evoluzione dell’interconnessione fisica Advanced Interface Bus (AIB). MDIO permette un approccio modulare alla progettazione del sistema con una libreria di blocchi di base (chiplet). “MDIO garantisce una migliore efficienza energetica e un bandwidth più che doppio per la velocità dei pin e la densità del bandwidth rispetto ad AIB”, aggiunge Intel.