Nel corso dell’evento Next Horizon Gaming a Los Angeles, AMD ci ha illustrato i dettagli dell’architettura Zen 2 alla base dei nuovi processori Ryzen 3000. Il CEO Lisa e il direttore tecnologico Mark Papermaster hanno esordito affermando che non si può parlare di Zen 2 senza citare i 7 nanometri.

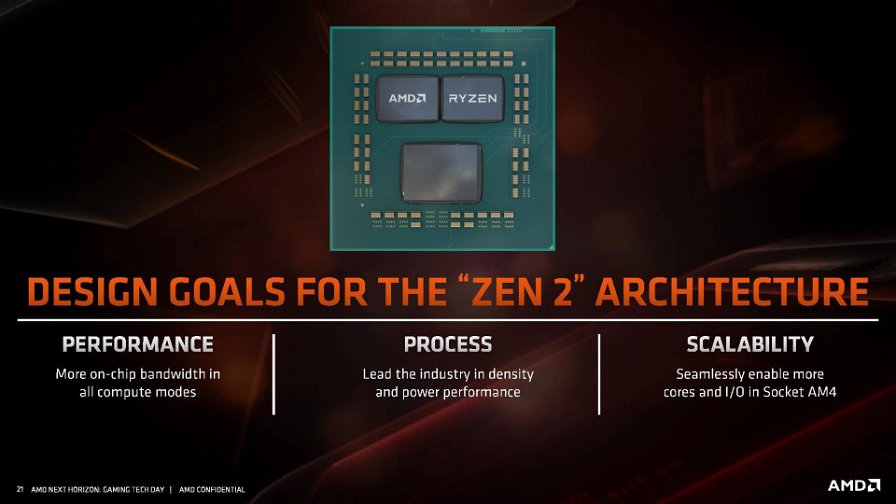

Sono due elementi indissolubili, perché tanto l’architettura quanto il processo produttivo sono nati e cresciuti in simbiosi per arrivare a garantire le prestazioni dichiarate da AMD per la sua nuova gamma di CPU. Il nuovo processo produttivo garantisce un raddoppio della densità, un dimezzamento dei consumi a parità di prestazioni oppure un aumento delle prestazioni del 25% a parità di consumi.

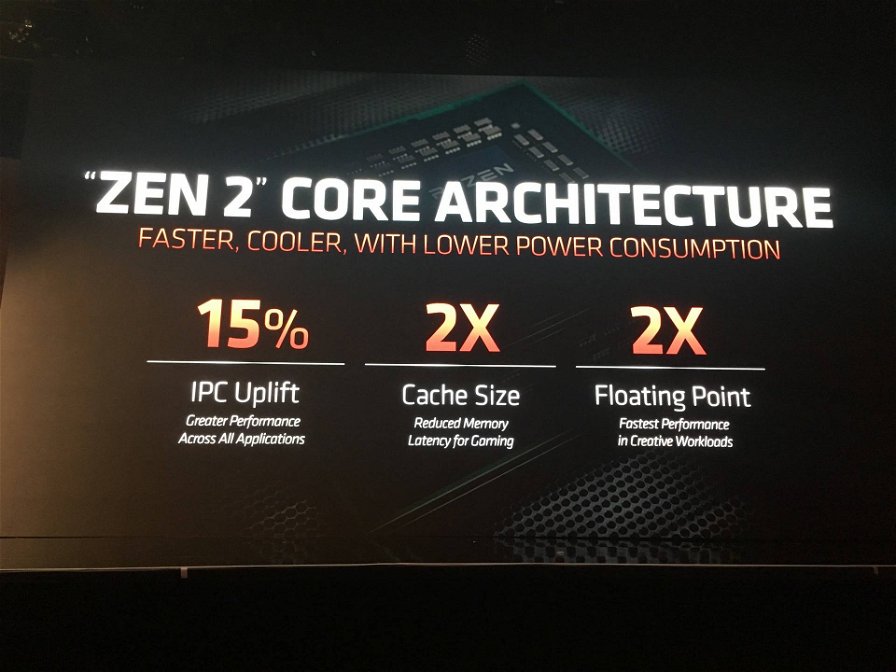

Sono tre i passi avanti fondamentali dell’architettura Zen 2: il miglioramento delle prestazioni IPC (istruzioni calcolate per ciclo di clock) del 15% rispetto Zen, cosa molto utile in ambito gaming, il raddoppio della dimensione della cache (dati più vicini ai core, minore latenza di memoria, più prestazioni in gaming) e prestazioni due volte maggiori con calcoli in virgola mobile (più prestazioni nei carichi di produttività) passando a due FPU a 256 bit che portano in dote il supporto alle istruzioni AVX2.

Andiamo con ordine. Con l’aumento dell’IPC del 15%, AMD afferma di aver fatto meglio dell'andamento tradizionale dell’industria e questo è stato possibile migliorando il branch predictor, il throughput integer, raddoppiando le prestazioni in virgola mobile e riducendo la latenza effettiva verso la memoria.

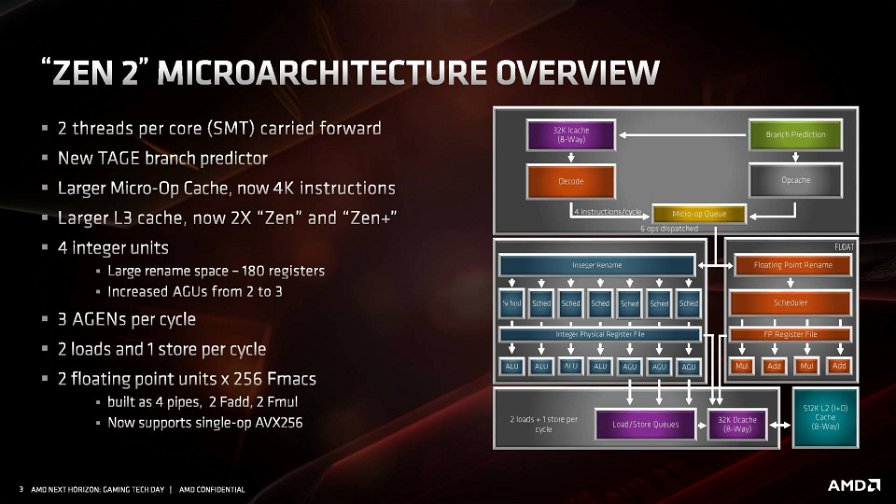

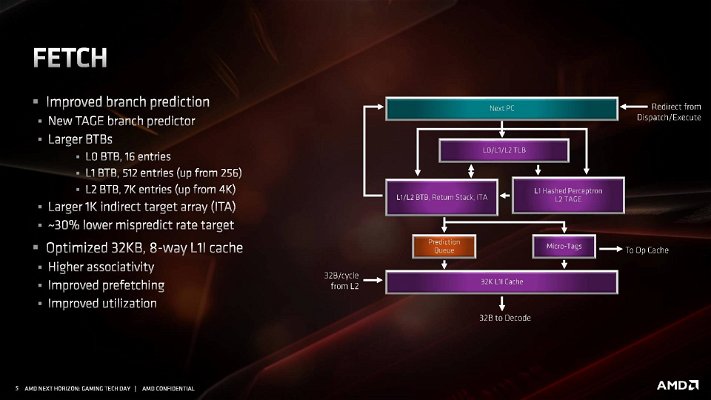

Per quanto riguarda il front-end, AMD ha introdotto un TAGE (Tagged Geometry) Branch Predictor più intelligente, rendendo il branch predictor a due stadi: il primo stadio formato dal tradizionale predictor Perception, mentre il secondo è appunto il nuovo TAGE branch predictor, caratterizzato da lookup table più ampie per migliorare le prestazioni.

Questo cambiamento impatta sui consumi del front-end, ma con un tasso di errore il 30% inferiore alla fine si risparmia molta più energia nel backend.

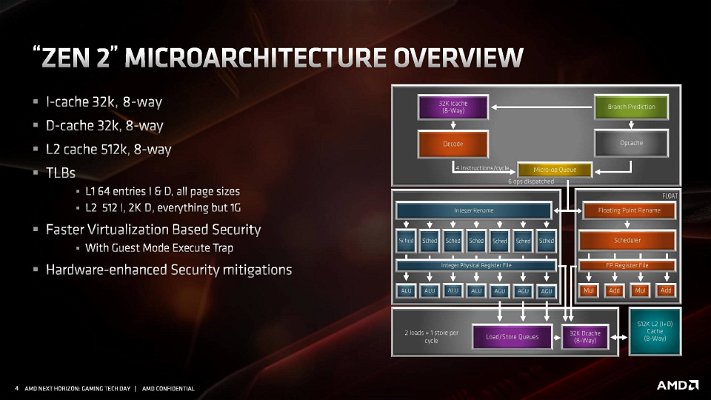

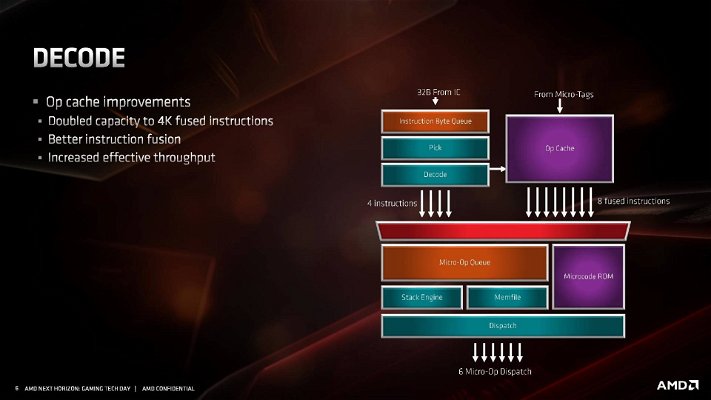

L'azienda ha migliorato il pre-fetching delle istruzioni, riottimizzato la cache instruction (32K 8-way associative contro 64K 4-way associative) e raddoppiato la op cache. AMD ha anche ampliato il Translation Lookaside Buffer (TLB) a 2000 entries.

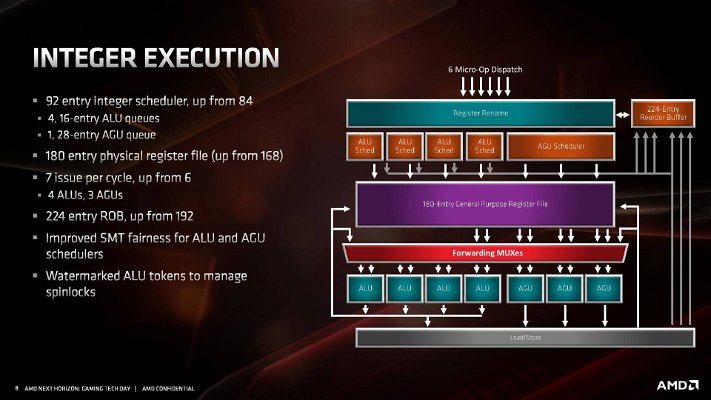

Passi avanti anche per quanto riguarda la parte integer, con uno scheduler in grado di gestire 92 istruzioni anziché 48, l'incremento del registro fisico da 168 a 180, un aumento degli issue per ciclo di clock da 6 a 7 e una migliorata equità dell’SMT con gli scheduler ALU e AGU.

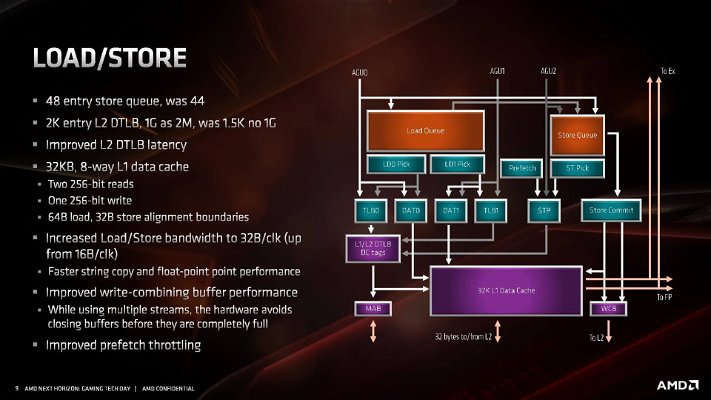

Altri miglioramenti riguardano l'aumento del bandwidth load / store da 16 B/clock a 32B/clock (con la store queue che passa da 44 a 48) e il passaggio da due a tre AGUs (Address Generation Units).

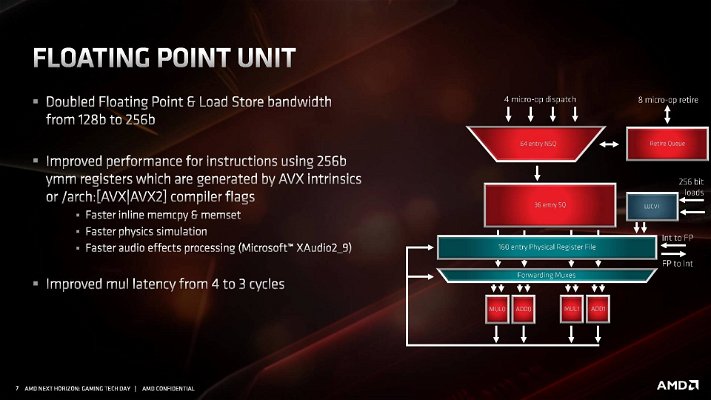

In merito ai progressi dell’unità floating point, AMD ha raddoppiato il bandwidth passando da 128 a 256 bit per ottenere un throughput superiore, introdotto il supporto ad AVX-256 e ridotto la contesa per quanto riguarda l’esecuzione integer.

AMD ha migliorato anche le cache, rendendole più intelligenti e andando a rinnovare la gerarchia. Non solo c’è un raddoppio della cache complessiva, che AMD chiama GameCache, ma il supporto anche a nuove istruzioni (CLWB, WBNOINVD, QOS) e una riduzione della latenza.

In tema di cache L3, questa serve ancora come victim cache per i dati della cache L2. E benché la cache più ampia aumenti leggermente i cicli di latenza, è proprio la sua capacità a compensare le perdite.

Per concludere, non si può non citare Infinity Fabric, spina dorsale dell'intera infrastruttura che permette ai dati di muoversi ad altissima velocità all'interno e all'esterno del chip. La seconda generazione vede alcuni miglioramenti per adattarsi meglio al mondo delle CPU client, come il disaccoppiamento di Fclk e Uclk (frequenza di clock della CPU e dell'uncore) per un miglior overclock della memoria e un miglioramento del consumo per bit del 27%.

[tomsgallery id=540001]

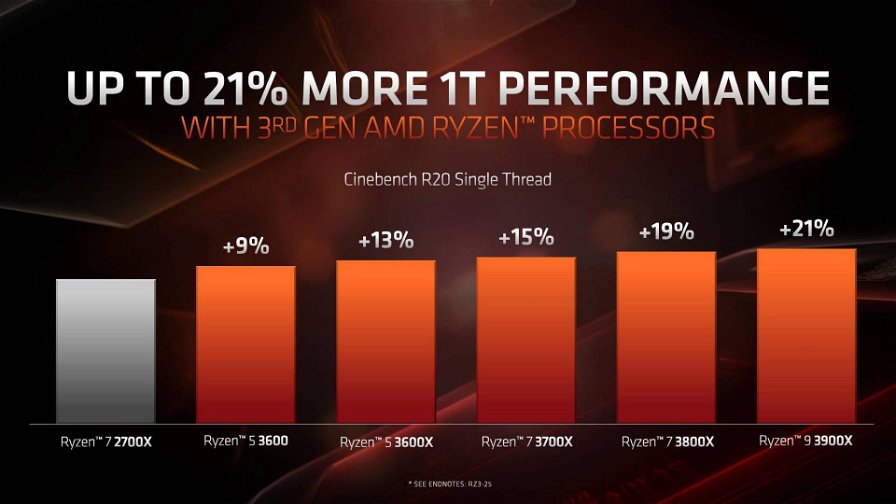

Tutto questo porta a un miglioramento delle prestazioni single-thread del 21% rispetto a Zen+, dei quali il 60% è riconducibile ai miglioramenti all’IPC e il resto alla frequenza e ai 7 nanometri.

Quando si parla di Zen 2 però non si può prescindere dal discutere del nuovo progetto basato sui chiplet, che vedete applicato a tutte le CPU senza grafica integrata, mentre le APU continuano ad adottare un progetto "standard".

Un processore Ryzen 3000 nella sua massima espressione è formato da due chiplet prodotti a 7 nanometri dove risiedono i core (otto per ciascun chiplet) e da un I/O die a 12 nanometri (e non 14 nanometri come dichiarato da AMD per EPYC 2), dove risiedono tutta la connettività, il controller di memoria, le linee PCIe 4.0 e così via.

Se pensiamo che un progetto simile, molto differente da quello delle due generazioni precedenti, adotta ancora il socket AM4, allora possiamo dire che AMD ha fatto quasi un mezzo miracolo. Nulla di impossibile, dato che ci è riuscita, ma conservando l'interfaccia è andata decisamente in controtendenza rispetto a Intel e quanto fatto dall'industria in passato. Se ripercorriamo la storia, praticamente l'AM4 ci accompagna dai tempo di Bristol Ridge, APU basata su architettura Excavator.

Non solo ha mantenuto l'interfaccia AM4 passando a un design basato su tre chip, con l'I/O disaccoppiata dai die della CPU, ma nel frattempo ha anche raddoppiato i core, mantenuto il funzionamento dei blocchi esistenti e introdotto anche il PCI Express 4.0.

Per questo anche il packaging e la progettazione fisica del processore hanno assunto un ruolo fondamentale. Con Ryzen 3000 AMD ha dovuto fare alcuni cambiamenti e adottare nuovi materiali per integrare il supporto PCIe 4.0. Questo a causa dei requisiti di signaling più stringenti del nuovo standard.

L'azienda ha scelto un materiale bassa perdita (low-loss) per i layer del package e questo ha consentito di conservare l'integrità del segnale. Nel complesso i Ryzen 3000 hanno quindi un package con un substrato a 12 layer al fine di gestire tutti collegamenti tra i vari elementi e l'esterno.

In termini di sicurezza AMD si è detta focalizzata nell’assicurare protezione dalle vulnerabilità che hanno colpito i microprocessori in questi ultimi due anni. Con Zen 2 l’azienda risolve in hardware Spectre V2 e Spectre V4, mentre continua a essere immune alle altre falle che invece hanno colpito le architetture Intel.

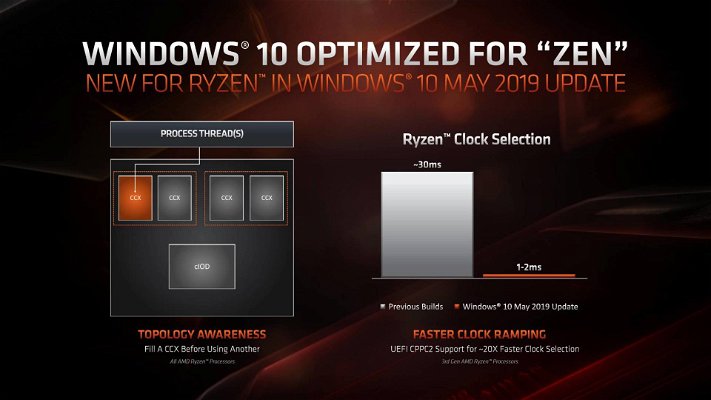

Un altro elemento in grado di dare “nuova linfa” all’architettura Zen 2 arriva dal software, con la nuova versione di Windows 10 (May 2019 Update, anche conosciuta come 1903) che è stata ottimizzata per sfruttare appieno la nuova architettura.

Ad esempio è in grado di usare completamente un CCX prima di suddividere il carico su più CCX e grazie alla funzionalità UEFI CPPC2 può aumentare più velocemente la frequenza dallo stato idle, con una risposta che passa da 30 millisecondi a soli 1-2 millisecondi.

In questo modo le latenza si riducono, il processore passa più rapidamente all'azione e in modo altrettanto veloce torna in idle. Insomma, grazie all'ottimizzazione migliorano tanto le prestazioni quanto i consumi.

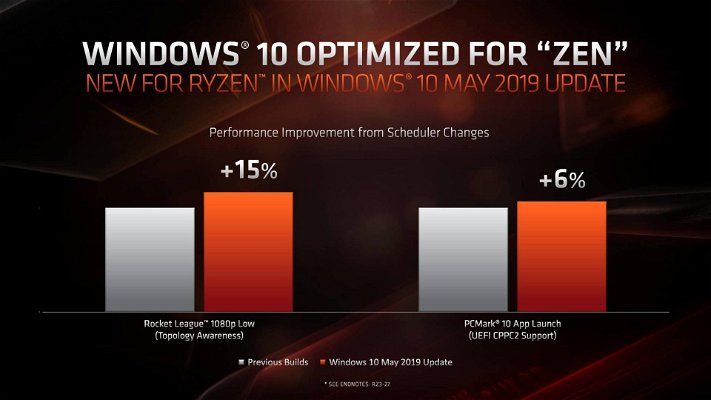

Più precisamente, secondo AMD, la capacità di Windows 10 di sfruttare la topologia può portare a miglioramenti prestazionali a doppia cifra, mentre la capacità di passare più rapidamente dall’idle alla frequenza di picco permette un aumento prestazionale intorno al 5%.

E se tutto questo non bastasse, AMD ha già le idee molto chiare per il futuro: l'azienda ha ribadito che l'architettura Zen 3 sta rispettando la tabella di marcia e Zen 4 è in fase di progettazione.