AMD, durante la conferenza Hot Chips 33, ha svelato ulteriori dettagli sulla tecnologia 3D V-Cache che farà parte dei nuovi chip basati su architettura Zen 3, in produzione quest’anno e in vendita nel 2022.

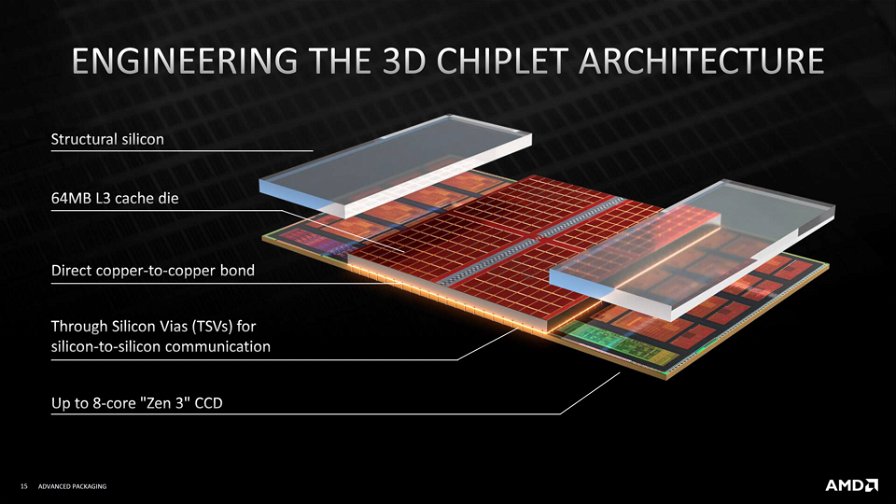

Secondo AMD, il 2021 segnerà la prima introduzione della sua architettura 3D Chiplet. Abbiamo già visto packaging 2D e 2.5D su prodotti consumer e server, ma con 3D V-Cache, finalmente entreremo nello stacking 3D. 3D Chiplet infatti significa che la memoria SRAM è impilata verticalmente sopra al core complex die, il CCD. L'uso della tecnologia chiplet 3D aumenta anche la densità di interconnessione pur mantenendo una potenza bassa.

Il CEO di AMD, Lisa Su, aveva già anticipato la tecnologia durante il Computex 2021. In quel caso aveva mostrato il prototipo di chip Ryzen 9 5900X funzionante, evidenziando le migliori performance ottenibili in ambito gaming, pari, in questo caso, ad una media del 15% a risoluzione 1080p. Mettendo a confronto il prototipo del Ryzen 9 5900X con la nuova 3D V-Cache contro un 5900X standard, con entrambi i chip bloccati a una velocità di clock di 4,0GHz, sono state registrate prestazioni migliori del 12% su Gears 5, e un guadagno medio del 15% in titoli come Dota 2, Monster Hunter World, League of Legends e Fortnite.

AMD, come riporta WCCFTech, ha ora condiviso nel dettaglio come integra la V-Cache 3D sul suo CCD Zen 3. Ciò si ottiene attraverso l'uso di diverse interconnessioni verticali TSV, che consentono di arrivare sino a 2TB/s di larghezza di banda tra il chip e la cache. L'interconnessione utilizza un nuovissimo collegamento dielettrico idrofilico diretto rame su rame che è stato progettato e co-ottimizzato in stretta collaborazione con TSMC. I due singoli chip sono legati insieme utilizzando questa tecnologia.

Secondo AMD, il legame ibrido ha un "pitch", ovvero la distanza tra i vari collegamenti TSV, di 9 micron, che è leggermente più piccolo dell'interconnessione Forveros di Intel che ha un passo di 10 micron. L'efficienza energetica dell'interconnessione è 3 volte superiore rispetto alle implementazioni Micro Bump 3D, e la densità dell'interconnessione è invece 15 volte superiore.

AMD sottolinea anche questo è solo l'inizio di ciò che potrebbero ottenere con lo stacking 3D. In futuro, AMD prevede di sfruttare lo stacking 3D per impilare CPU sopra CPU, i core sopra i core, l'IP sopra l'IP e le cose potrebbero diventare davvero sempre più pazzesche.